4.8 PCI Express Root Complex

4.8.1 Introduction

i.MX SoC에 포함된 PCI Express 하드웨어 모듈은 Root Complex나 PCIe Endpoint로 작동하도록 구성할 수 있다. 이 문서는 i.MX SoC 계열에서 PCI Express Root Complex 구현 설명에 사용된다. 또한 i.MX PCI Express 디바이스에서 Root Complex로 구성되고 작동하는 데 필요한 드라이버에 대해 설명한다.

PCI Express (PCIe)는 Third Generation I/O Interconnect로 저비용, 대용량, 다중 플랫폼 상호 연결 사용을 목표로 한다. 이전 PCI와 PCI-X 같은 개념을 가지며, 아래와 같은 차이점이 있는 기존 PCI 소프트웨어에 대한 하위 호환성을 제공한다 :

- PCIe는 point-to-point(지점 간) 상호 연결이다.

- 디바이스 사이에 시리얼 링크

- 패킷 기반의 통신

- x1에서 x16까지의 Lanes의 집합을 통한 스케일 가능한(scalable) 성능

- 두 개 이상의 PCIe 디바이스를 연결하려면, PCIe 스위치가 필요하다.

4.8.2 Terminology and Conventions

이 문서에는 아래 용어와 규칙을 사용한다 :

- Bridge

내부 컴포넌트 상호 연결이나 다른 PCI/PCI-X 버스 세그먼트나 PCI Express Port와 함께 PCI/PCI-X 세스먼트나 PCI Express Port를 가상이나 실제로 연결하는 기능이다. - Downstream

- Root Complex에서 더 멀리 있는 interconnect/System Element(Port/component)의 상대 위치이다. Upstream Port가 아닌 Switch의 Port는 Downstream Port이다. Root Complex의 모든 Port는 Downstream Port이다. Link의 Downstream 컴포넌트는 Root Complex에서 더 먼 컴포넌트이다.

- 정보가 Root Complex에서 멀어지는 정보 흐름의 방향이다.

- Endpoint

정의된 여러 System Elements 중 하나이다. Type 00h Configuration Space 헤더가 있는 기능이다. - Host

Root Complex를 통해 연결된 여러 PCIe 노드에서 공유할 수 있는 메모리(RAM)와 같은 리소스와 하나(또는 그 이상) Central Processing Unit(CPU)로 구성된 엔터티(entity)이다. - Lane

차동 신호 쌍의 세트, 한 쌍은 전송용이고 다른 한쌍은 수신용이다. - Link

두 개의 Port와 상호 연결되는 Lane의 컬렉션이다. Link는 두 컴포넌트 사이의 이중 단반향(dual simplex) 통신 경로이다. - PCIe Fabric

디바이스라고도 하는 다양한 PCI Express 노드로 구성되는 토폴로지. 패브릭에서 디바이스는 Root Complex, Endpoint, PCIe-PCI/PCI-X Bridge 또는 Switch가 될 수 있다. - Port

- 논리적으로, 컴포넌트와 PCI Express Link 사이의 인터페이스이다.

- 물리적으로, 링크를 정의한 동일 칩에 위치한 송신기와 수신기의 그룹이다.

- Root Complex

Host Bridge, 0개 이상의 Endpoint 통합 Root Complex, 0개 이상의 Root Complex Event Collector와 하나 이상의 Root Port를 포함하는 System Element 정의된 RC. - Root Port

연결된 가상 PCI-PCI Bridge를 통해 Hierarchy(계층 구조)의 일부를 매핑하는 Root Complex의 PCI Express Port이다. - Upstream

- Root Complex에서 더 가까운 interconnect/System Element (Port/component)의 상대 위치이다. Root Complex에서 토폴로지상 가장 가까운 Switch의 Port는 Upstream Port이다. Endpoint나 Bridge Function만 포함하는 컴포넌트의 Port는 Upstream Port이다. Link에서 Upstream 컴포넌트는 Root Complex에서 더 가까운 컴포넌트이다.

상대적으로 RC에 더 가까운 패브릭의 요소는 'Upstream'으로 처리된다. RC에 더 가까운 모든 PCIe Endpoint port(bridge에 대한 termination point 포함)와 Switch port는 해당 디바이스에서 Upstream Port라고 한다. Upstream Flow는 RC로 이동하는 통신이다.

4.8.3 PCIe Topology on i.MX

i.MX에는 PCIe 포트가 하나 있다. 현재, Linux BSP에서는 RC 모드만 활성화 되어 있다.

아래 그림은 i.MX에서 PCIe RC 포트의 다이어그램을 설명한다.

PCI Enumeration Mapping

PCI Express는 point-to-point 토폴로지이므로, Software Enumeration에 사용되는 레거시 PCI Bus - Device 개념과 호환성을 유지하기 위해 PCI 디바이스/기능 측면에서 다양한 노드와 그 내부(예: PCIe Switch)를 식별할 수 있는 아래의 개념을 도입한다 :

- Host Bridge: Host에 호환성 있는 PCI 연결을 위해 RC에 통합된 브리지이다. 이 브리지의 PCI 방향은 항상 Bus #0 이다. 즉, 이 버스에서 디바이스는 호스트 자체가 된다.

- Virtual PCI-PCI Bridge: RC나 Switch의 일부인 각 PCI Express 포트는 가상의 PCI-PCI 브리지로 처리된다. 즉 각 포트는 기본(primary)과 보조(secondary) PCI 버스가 있고 다운스트림은 원격 구성 공간에 매핑된다.

- 가상 브리지와 연결된 Root Port는 다운스트림에서 보조(secondary) 버스와 기본(primary)에서 Bus #0을 가진다.

- 각 PCIe Switch는 실제로 Switch의 업스트립 포트를 형성하는 다른 PCI-PCI 브리지의 보조(secondary) 버스인 가상의 PCI 버스에 연결된 다운스트림 포트의 수 만큼 많은 가상의 PCI-PCI 브리지의 컬렉션으로 간주된다.

- 각 EP의 업스트림 포트는 Switch나 Root Port의 다운스트림 포트를 나타내는 가상의 PCI-PCI Bridge의 보조(secondary) 버스 세스먼트의 일부일 수 있다.

4.8.4 Features

다음은 i.MX에서 PCI Express Root Complex 드라이버로 지원하는 다양한 기능이다.

- Express Base Specification Revision 2.0 호환

- 단일 방향에서 5 GT/s의 로우(raw) 전송 속도를 지원하는 x1 링크로 Gen2 작동.

- Legacy Interrupts (INTx)와 MSI 지원.

- Max_Payload_Size 크기 (128 바이트).

- 호한되는 PCI 소프트웨어 열거 지원을 제공하기 위해 Linux PCI Bus 프레임워크에 맞춘다.

- 또한 다운스트림에서 감지된 각 디바이스에 액세스하도록 Endpoint Driver에 인터페이스를 제공한다.

- AER, ASP 등을 처리하기 위해 Linux OS의 PCI Express Port Bus Driver 프레임워크에서 동일한 인터페이스를 사용할 수 있다.

- Legacy Interrupts(INTx)로 EP 드라이버를 위한 인터럽트 처리 기능.

- Linux PCI 서브시스템의 일반 I/O 부분으로 EP I/O BAR에 액세스한다.

- PCIe 오류의 원활한 처리.

- L0, L0s, L1과 L1.1 ASPM 전원 관리를 지원.

4.8.5 Linux OS PCI Subsystem and RC driver

Linux OS에서 PCI 구현은 대충 Linux OS에서 아키텍처별로 구현한 PCI BIOS, Host Controller (RC) Module, Core의 주요 컴포넌트로 나눌 수 있다.

- PCI 버스 초기화를 시작하는 PCI BIOS Architecture-specific Linux OS 구현. PCI Host Controller 코드와 PCI Core를 인터페이스하여 버스 열거와 메모리 및 인터럽트와 같은 리소스 할당을 수행한다. BIOS 실행이 성공적으로 완료되면, 시스템의 모든 PCI 디바이스에 사용 가능한 PCI 리소스의 일부와 해당 드라이버(Slave Driver라고 함)가 할당된다. PCI는 PCI Core에서 제공하는 기능을 사용하여 컨트롤할 수 있다. 리소스 할당은 건너뛸 수 있다(예로 PC 시나리오와 같이 Linux OS가 부팅되기 전에 할당된 경우).

- Host Controller (RC) Module은 특정 하드웨어(SoC + Board) 초기화와 구성을 처리하고 PCI BIOS를 호출한다. BIOS와 PCI Core에 대해 콜백 함수를 제공해야 하며, 이는 PCI 시스템 초기화하는 동안과 PCI 버스에 액세스하는 구성(configuration) 동안 호출된다. 사용 가능한 메모리 I/O 공간, INTx 인터럽트 라인, MSI에 대한 리소스 정보를 제공한다. 또한 in _x_ () out _x_ ()로 IO 공간 액세스(지원되는 대로)를 용이하게 제공해야 한다. read _x_ () write _x_ ()로 간접 메모리 액세스(h/w에서 지원하는 경우)를 제공해야 할 수 도 있다.

- Core는 시스템의 브리지와 버스 디바이스에 대해 데이터 구조 트리를 생성 및 초기화하고, 버스/디바이스 번호 지정을 처리하고, 디바이스 항목과 proc/sysfs 정보를 생성하고, BIOS와 슬레이브 드라이버에 대한 서비스를 제공하고, 핫 플러그 지원(선택사항 h/w에서 지원)을 제공한다. EP 드라이버 인터페이스 쿼리를 대상으로 열거(enumeration) 중에 발견된 해당 디바이스를 초기화한다. 또한 MSI 인터럽트 처리 프레임워크와 PCI Express 포트 버스 지원을 제공한다. Hot-Plug 지원(지원되는 경우), 고급 오류 보고 지원, 전원 관리 이벤트 지원, PCI Express 포트에서 실행되는 가상 채널 지원(지원되는 경우)을 제공한다.

4.8.6 PCIe Driver Source Files

Table 45. Source Files

| File | Description |

| drivers/pci/controller/dwc/pci-imx6.c | i.MX 6 PCIe 소스 |

4.8.7 System Resource: Memory Layout

- IO와 메모리 공간은 CPU상의 Linux 커널에서 실행되는 디바이스 드라이버와 통신하기 위해 디바이스가 사용하는 두 개의 주소 공간이다.

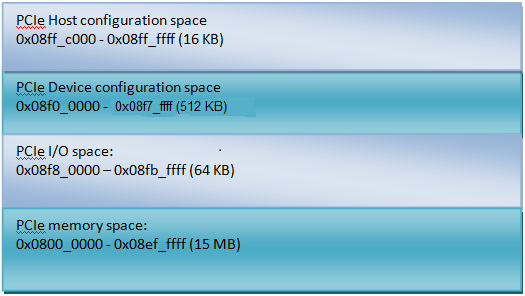

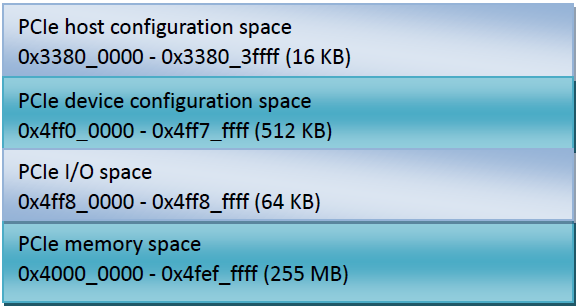

- 상위 16 KB PCIe 호스트 구성 공간.

- 이 메모리 세스먼트는 PCIe RC의 구성 공간 매핑에 사용된다. SW는 DBI 인터페이스로 PCIe RC core 구성 공간에 액세스할 수 있다.

- PCIe 디바이스 구성 공간

- RC 다운스트림 포트에 끼워 넣는 PCIe EP 디바이스의 구성 공간 매핑에 사용된다.

i.MX 8QuadMax/8QuadXPlus :

i.MX 8QuadMax에는 PCIeA와 PCIeB가 모두 있는 반면, i.MX 8QuadXPlus에는 PCIeB만 있다.

- PCIeA

- PCIe host configuration space: 0x5f00_0000 – 0x5f00_ffff (64K bytes)

- PCIe device configuration space: 0x6ff0_0000 – 0x6ff7_ffff (512K bytes)

- PCIe IO space: 0x6ff8_0000 – 0x6ff8_ffff (64K bytes)

- PCIe memory space: 0x6000_0000 – 0x6fef_ffff (255M bytes)

- PCIeB

- PCIe host configuration space: 0x5f01_0000 – 0x5f01_ffff (64K bytes)

- PCIe device configuration space: 0x7ff0_0000 – 0x7ff7_ffff (512K bytes)

- PCIe IO space: 0x7ff8_0000 – 0x7ff8_ffff (64K bytes)

- PCIe memory space: 0x7000_0000 – 0x7fef_ffff (255M bytes)

i.MX 8M Quad :

- PCIe0

- PCIe host configuration space: 0x3380_0000 – 0x33bf_ffff (4Mbytes)

- PCIe device configuration space: 0x1ff0_0000 – 0x1ff7_ffff (512K bytes)

- PCIe IO space: 0x1ff8_0000 – 0x1ff8_ffff (64K bytes)

- PCIe memory space: 0x1800_0000 – 0x1fef_ffff (127M bytes)

- PCIe1

- PCIe host configuration space: 0x33c0_0000 – 0x33ff_ffff (4Mbytes)

- PCIe device configuration space: 0x27f0_0000 – 0x27f7_ffff (512K bytes)

- PCIe IO space: 0x27f8_0000 – 0x27f8_ffff (64K bytes)

- PCIe memory space: 0x2000_0000 – 0x27ef_ffff (127M bytes)

4.8.8 System Resource: Interrupt lines

i.MX Root Complex 드라이버는 i.MX 6 플랫폼의 MSI INT에 152를, i.MX 7Dual 플랫폼의 MSI INT에 154 인터럽트 라인을 사용한다.

'NXP i.MX SoC Family > i.MX Linux Reference Manual' 카테고리의 다른 글

| i.MX Linux Reference Manual - Connectivity - USB3 (0) | 2022.08.01 |

|---|---|

| i.MX Linux Reference Manual - Connectivity - USB (6) | 2022.07.29 |

| i.MX Linux Reference Manual - Connectivity - Media Local Bus (0) | 2022.07.26 |

| i.MX Linux Reference Manual - Connectivity - Inter-IC (I2C) (0) | 2022.07.26 |

| i.MX Linux Reference Manual - Connectivity - FlexCAN (0) | 2022.07.25 |