3 MIPI CSI-2 Rx subsystem

이 섹션에서는 CSI-2 Rx DPHY와 호스트 컨트롤러가 있는 i.MX 8M 시리즈 MIPI CSI-2 Rx 서브시스템을 소개한다. CSI-2 Rx DPHY와 호스트 컨트롤러는 MIPI CSI-2 사양에 정의된 모든 프로토콜 기능을 구현하는 디지털 코어로, 호스트 프로세서와 MIPI CSI-2 호환 카메라 센서 사이의 인터페이스를 제공한다.

i.MX 8MM과 i.MX 8MN에서는 이 서브시스템의 하나의 인스턴스는 모든 입력 이미징 디바이스에 대한 센서/이미지 입력과 프로세스를 처리하는 이미징 서브시스템에 연결된다. i.MX 8MQ와 i.MX 8MP에 구현된 MIPI CSI-2 Rx 서브시스템에는 두 개의 인스턴스가 있다. 이 문서에서는 CSI-2 Rx 서브시스템의 단일 인스턴스를 지정한다.

i.MX 8MM/i.MX 8MN/i.MX 8MP는 CSI-2 Rx DPHY와 호스트 컨트롤러 IP를 공유하지만, i.MX 8MQ는 다른 IP를 사용한다.

3.1 i.MX 8MQ MIPI CSI-2 Rx subsystem

이 섹션에서는 i.MX 8MQ의 MIPI CSI-2 Rx 서브시스템을 소개한다.

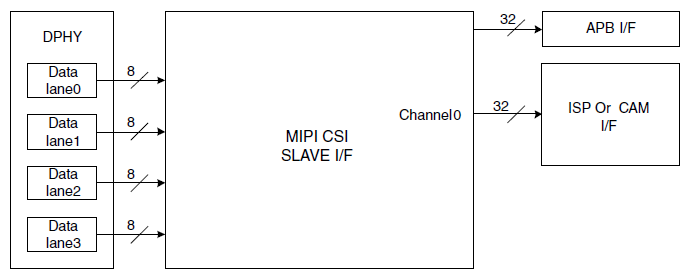

Figure 1은 i.MX 8MQ의 MIPI CSI-2 Rx 서브시스템에 대한 블럭 다이어그램을 보여준다.

3.1.1 Features

i.MX 8MQ MIPI CSI-2 Rx 서브시스템에는 다음과 같은 주요 기능이 있다:

- MIPI D-PHY와 CSI-2 Specification Version 1.1 준수

- 1개의 클럭 레인과 최대 4개의 데이터 레인으로 구성

- 고속(hogh-speed)과 저전력(low-power) 모드 모두 지원

- 고속 모드에서 레인당 80Mbps ~ 1.5Gbps 데이터 속도 지원

- 저전력 모드에서 10Mbps 데이터 속도 지원

- primary와 secondary 이미지 포맷 지원

- YUV420, YUV420 (Legacy), YUV420 (CSPS), 8비트, 10비트의 YUV422

- RGB565, RGB666, RGB888

- RAW6, RAW7, RAW8, RAW10, RAW12, RAW14

- All User-Defined Byte-based Data packet (사용자 정의 바이트 기반 데이터 패킷)

- Hsync와 Vsync로 비디오 데이터 출력을 지원

3.1.2 Configuration port

i.MX 8MQ CSI-2 Rx 컨트롤 코어에는 실시간으로 코어의 구성을 제어할 수 있는 구성(configuration) 포트가 있다. 포트는 Table 2에 나열되어 설명되고 있다. CSR 모듈이 CSI-2 Rx 컨트롤러의 일부인 경우, cfg_* 포트가 최상위 레벨에서 제거되고 CSR 모듈의 포트에 연결되어 APB 인터페이스를 사용하여 액세스할 수 있다.

Table 2. i.MX 8MQ CSI-2 Rx controller core configuration port

| Port | Type | Description |

|---|---|---|

| cfg_num_lanes[1:0] | Input | MIPI 데이터 수신에 사용할 활성(active) 레인 수를 설정한다. [0] –1 Lane [1] – 2 Lanes [2] – 3 Lanes [3] – 4 Lanes |

| cfg_disable_data_lanes[3:0] | Input | 비트를 '1'로 설정하면, DPHY Enable 신호가 비활성화된다. [0] – data lane 0 [1] – data lane 1 [2] – data lane 2 [3] – data lane 3 |

3.1.3 Clocking constraint

i.MX 8MQ CSI-2 Rx 컨트롤러 코어는 clk_ui와 clk의 적절한 작동을 위해 2개의 클럭이 필요하다. clk_ui 클럭은 사용자 인터페이스와 동기되는 클럭으로, 모든 입력과 출력은 clk_ui의 상승 에지를 참조한다. clk 입력은 CSI-2 Rx 컨트롤러 코어가 D-PHY에서 수신한 데이터를 처리하는 데 사용하는 클럭이다.

Table 3은 클럭 포트와 대역폭 요구 사항을 설명한다.

Table 3. i.MX 8MQ CSI-2 Rx controller clock

| Clock name | Description |

|---|---|

| clk (MIPI_CSIx_CORE_CLK) | Rx 컨트롤러 Core Clock (Byte Clock). clk는 Rx DPHY의 데이터 레인 0, 1, 2, 3에서 오는 수신된 바이트 클럭(RxByteClkHS%)보다 크거나 같아야 한다. |

| clk_ui (MIPI_CSIx_PHY_REF_CLK) | User Interface Clock (Pixel Clock). clk_ui는 CSI-2 MIPI 인터페이스에서 들어오는 데이터보다 크거나 같아야 한다. |

| clk_esc (MIPI_CSIx_ESC_CLK) | Rx Escape Clock. Rx DPHY가 수신하는 것과 동일한 이스케이프 클럭이어햐 한다. |

clk_ui의 최소 주파수는 CSI-2 MIPI 인터페이스의 수신 데이터 속도를 따라갈 수 있을 만큼 충분히 높아야 한다. 사용자 인터페이스는 픽셀 기반이므로 MIPI Rx DPHY에서 들어오는 바이트 데이터보다 더 넓을 수 있다는 점을 인식하는 것이 중요하다. 예를 들어 RGB888 데이터가 수신되는 경우, 사용자 인터페이스 데이터 폭은 24비트(clk_ui 상승 에지당 1픽셀, 각 픽셀은 24비트)가 된다. 예를 들어 MIPI 인터페이스를 단일 레인에서 1000Mbps로 실행하도록 한다. CSI-2 Rx 컨트롤러에 대한 데이터 속도는 125Mbps이므로, clk는 125MHz 이상에서 실행되어야 한다. 사용자 인터페이스의 너비가 3바이트이므로 clk_ui는 들어오는 데이터를 따라잡기 위해 125MHz/3 이상에서 실행해야 한다.

3.1.4 Configuration procedure

i.MX 8MQ MIPI CSI-2 Rx 서브시스템의 리셋과 초기화 절차는 다음과 같다:

- 모든 리셋을 어설트한다.

- Rx 컨트롤러에 대한 클럭이 안정화될 때까지 기다렸다가 DPHY 인터페이스가 유휴 상태인지 확인한다(모든 레인에서 Stop State).

- CSR이 컨트롤러에 포함된 경우, CSR, pclk_reset_n으로 리셋을 해제한다. CSR이 없는 경우 4 단계로 이동한다.

- CSR이 있으면, CSR 레지스터를 프로그램한다. CSR이 없으면, 모든 구성 포트(cfg_*inputs)의 값을 적절한 값으로 설정한다.

- 데이터 레인 수(레지스터 CSI2RX_CFG_NUM_LANES와 CSI2RX_CFG_DISABLE_DATA_LANES)

- 인터럽트 마스크 (레지스터 CSI2RX_IRQ_MASK)

- hs_settle과 같은 PHY 설정 (PRG_RXHS_SETTLE 레지스터 필드, Section 3.1.5 참조)

- 남아 있는 모든 리셋을 해제한다.

- clk_ui의 다음 상승 에지에서 i.MX 8MQ CSI-2 Rx 컨트롤러를 사용할 준비가 되었다.

3.1.5 DPHY high-speed settle timer

Table 4와 Table 5는 PRG_RXHS_SETTLE [5:0]에 대한 값을 계산하는 방법을 설명한다.

Table 4. High-speed settle timer range

| Min (ns) | Max (ns) | |

|---|---|---|

| THS-SETTLE | 85 ns + 6*UI | 145 ns + 10*UI |

Table 5. PRG_RXHS_SETTLE setting for different data rates

| Data rate | Min (ns) | Max(ns) | PRG_RXHS_SETTLE[5:0] | THS-SETTLE (ns) |

|---|---|---|---|---|

| 1.5 Gbps | 89 | 151.67 | 000110 | 106.06 |

| 1.0 Gbps | 91 | 155 | 000110 | 106.06 |

| 500 Mbps | 97 | 165 | 000110 | 106.06 |

| 250 Mbps | 109 | 185 | 001000 | 136.36 |

| 80 Mbps | 160 | 270 | 001011 | 181.82 |

|

||||

3.1.6 Register definition

이 섹션에서 사용자가 새로운 카메라를 포팅하기 위해 주의해야 하는 일부 레지스터 필드들이 나열되어 있다. 레지스터에 대한 더 많은 정보는 i.MX 8MQ Reference Manual을 참조한다.

i.MX 8MQ MIPI CSI-2 컨트롤러의 기본 주소는 다음과 같다:

- CSI-2 Port 1: 30A7_0000h

- CSI-2 Port 2: 30B6_0000h

▶ CSI2RX_CFG_NUM_LANES 레지스터: 100h 오프셋

Table 6. CSI2RX_CFG_NUM_LANES register

| Field | Description |

|---|---|

| 1-0 csi2rx_cfg_num_lanes |

데이터 수신에 사용할 활성(active) 레인 수를 설정한다. 00b - 1 Lane 01b - 2 Lane 10b - 3 Lane 11b - 4 Lane |

▶ CSI2RX_CFG_DISABLE_DATA_LANES 레지스터: 104h 오프셋

Table 7. CSI2RX_CFG_DISABLE_DATA_LANES register

| Field | Description |

|---|---|

| 3-0 csi2rx_cfg_disable_data_lanes |

비트를 '1'로 설정하면, DPHY Enable 신호가 비활성화된다. 0001b - Data Lane 0 0010b - Data Lane 1 0100b - Data Lane 2 1000b - Data Lane 3 |

▶ CSI2RX_IRQ_STATUS 레지스터: 10Ch 오프셋

Table 8. CSI2RX_IRQ_STATUS register

| Field | Description |

|---|---|

| 8-0 csi2rx_irq_status |

CSI2 RX IRQ 상태 [0] – crc error [1] – one-bit ecc error [2] – two-bit ecc error [3] – ULPS status change [4] – DPHY ErrSotHS has occurred [5] – DPHY ErrSotSync_HS has occurred [6] – DPHY ErrEsc has occurred [7] – DPHY ErrSyncEsc has occurred [8] – DPHY ErrControl has occurred |

▶ CSI2RX_IRQ_MASK 레지스터: 110h 오프셋

Table 9. CSI2RX_IRQ_MASK register

| Field | Description |

|---|---|

| 8-0 csi2rx_irq_mask |

CSI2 RX IRQ 마스크 설정 IRQ_MASK의 각 비트는 IRQ_STATUS의 각 비트에 대응한다. IRQ_MASK의 비트를 1로 설정하면 IRQ_STATUS의 해당 비트를 마스크하여 irq_out이 어설트되지 않도록 한다. |

▶ CSI-2 Port 1용 IOMUXC_GPR_GPR34 레지스터: 3034_0088h

▶ CSI-2 Port 2용 IOMUXC_GPR_GPR41 레지스터: 3034_00A4h

Table 10. IOMUXC_GPR_GPR34/41 register

| Field | Description |

|---|---|

| 7-2 CSI2_x_S_PRG_RXHS_SETTLE |

MIPI CSI2_x D-PHY 프로그램 T_HS_SETTLE비트. HS-RX는 전환 효과를 무시하기 위해 Time-out T_HS_SETTLE을 기다린다. Section 3.1.5, “DPHY High-Speed Settle Timer”를 참조한다. |

3.2 i.MX 8MM/i.MX 8MN/i.MX 8MP MIPI CSI-2 Rx subsystem

이 섹션에서는 i.MX 8MM, i.MX 8 MN, i.MX 8MP의 MIPI CSI-2 Rx 서브시스템을 소개한다.

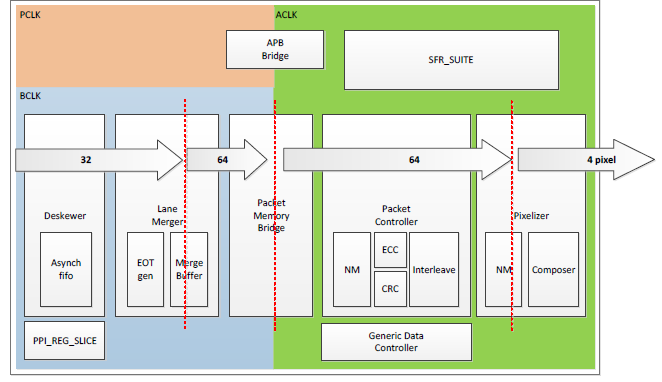

Figure 2는 i.MX 8MM/i.MX 8MN/i.MX 8MP의 MIPI CSI-2 Rx 서브시스템에 대한 블럭 다이어그램을 보여준다. MIPI CSI-2 Rx 컨트롤러(CSIS V3.6.3)는 카메라를 호스트 프로세스에 연결하기 위해 MIPI Rx DPHY 모듈과 함께 작동한다.

Figure 3은 i.MX 8MM/i.MX 8MN/i.MX 8MP의 CSIS V3.6.3 Slave Module에 대한 블럭 다이어그램을 보여준다.

3.2.1 Features

i.MX 8MM/i.MX 8MN/i.MX 8MP MIPI CSI-2 Rx 서브시스템에는 다음과 같은 주요 기능이 있다:

- MIPI D-PHY Specification Version 1.2 준수

- MIPI CSI-2 Specification Version 1.3 준수

- 1개의 클럭 레인과 최대 4개의 데이터 레인으로 구성

- 고속(hogh-speed)과 저전력(low-power) 모드 모두 지원

- 고속 모드에서 레인당 80Mbps ~ 1.5Gbps 데이터 속도 지원

- 저전력 모드에서 10Mbps 데이터 속도 지원

- primary와 secondary 이미지 포맷 지원

- YUV420, YUV420 (Legacy), YUV420 (CSPS), 8비트, 10비트의 YUV422

- RGB565, RGB666, RGB888

- RAW6, RAW7, RAW8, RAW10, RAW12, RAW14

- All User-Defined Byte-based Data packet (사용자 정의 바이트 기반 데이터 패킷)

- Hsync와 Vsync로 비디오 데이터 출력을 지원

- ppi 데이터가 오지 않을 때, 픽셀 클럭을 게이트할 수 있다.

3.2.2 ISP/CAM interface

CSIS V3.6.3 ISP나 CAM 인터페이스는 PIX_CLK, VVALID, HVALID, BVALID, DATA(Section 3.2.2에서 설명)인 출력 신호를 갖는다. 모든 신호는 PIX_CLK의 상승 에지와 동기화된다.

Table 11. CSIS V3.6.3 ISP/CAM interface port

| Port | Type | Description |

|---|---|---|

| PIX_CLK | Output | 픽셀 클럭. 이 신호는 I_ACLK에서 생성된다. |

| VVALID | Output | 수직 sync 신호. 이 신호는 전체 프레임 동안 설정된다. |

| HVALID | Output | 수평 sync 신호. 이 신호는 각 라인에서 설정된다. |

| BVALID | Output | 바이트 유효 신호. 이 신호는 유효한 바이트 수를 나타내며, Use defined type와 Parallel 모드에서만 유효하다. |

| DATA | Output | 픽셀 데이터 버스. 픽셀은 데이터 유형에 따라 정렬된다. |

3.2.3 Clocking constraint

MIPI CSI는 I_RxByteClkHs%, I_ACLK, I_PCLK의 3 가지 클럭 소스가 있다.

Table 12는 클럭 포트와 대역폭 요구 사항을 설명한다.

Table 12. CSIS V3.6.3 Clock

| Clock name | Description |

|---|---|

| I_RxByteClkHs% | 바이트 클럭. 이 클럭은 Rx DPHY의 데이터 레인 0, 1, 2, 3에서 가져온다. |

| I_ACLK | 픽셀 클럭. 이 클럭은 ISP/CAM 인터페이스를 사용하기 위한 픽셀 클럭용 외부 클럭이다. |

| I_PCLK | APB 클럭. 이 클럭은 일반 프로세서의 PLL에서 생성되는 시스템 클럭이다. |

입력과 출력 대역폭의 관계는 출력 대역폭이 입력 대역폭보다 빨라야 한다는 것이다. 이전 관계의 방정식이 있다:

RX_BYTE_CLK_HS x NUMBER_OF_DATA_LANE x 8BITS ≤

PIXEL_CLOCK x BITWIDTH_OF_IMAGE_FORMAT x NUMBER_OF_PIXEL_PER_CLOCK

3.2.4 Configuration procedure

i.MX 8MM/i.MX 8MN/i.MX 8MP MIPI CSI-2 Rx 서브시스템의 리셋과 초기화 절차는 다음과 같다:

- SW 리셋을 어설트한다. 소프트웨어 리셋이 완료되면 자동으로 해제된다.

- DPHY 구성:

- DPHY 슬레이브 컨트롤 (레지스터 MIPI_CSIx_DPHY_SLAVE_CTRL_LOW)

- DPHY 마스터와 슬레이브 컨트롤 (레지스터 MIPI_CSIx_DPHY_MASTER_SLAVE_CTRL_LOW/HIGH)

- 데이터 레인 0/1/2/3 활성화, HS settle 타이머 설정과 같은, DPHY 공통 컨트롤 (레지스터 MIPI_CSIx_DPHY_COMMON_CTRL)

- CSIS 구성:

- 인터럽트 마스크 (레지스터 MIPI_CSIx_INTERRUPT_MASK_0)

- 이미지 데이터 유형, 수직/수평 이미지 해상도와 같은, CAM/ISP 인터페이스 설정 (레지스터 MIPI_CSIx_ISP_CONFIG0, MIPI_CSIx_ISP_RESOLUTION0, MIPI_CSIx_ISP_SYNC0)

- CSIS 클럭 컨트롤 (레지스터 MIPI_CSIx_CSIS_CLOCK_CTRL)

- 데이터 레인 수와 같은, CSIS 공통 컨트롤 (레지스터 MIPI_CSIx_CSIS_COMMON_CTRL)

- Gasket 구성(i.MX 8 MN과 i.MX 8MP만 해당):

- 데이터 유형, 인터페이스 모드와 같은, Gasket 컨트롤 (레지스터 GPR_GASKET_x_CTRL)

- Gasket 비디오 크기 설정 (레지스터 GPR_GASKET_x_HSIZE, GPR_GASKET_x_VSIZE)

참고: i.MX 8 MN, i.MX 8MP에는 MIPI CSI-2 Rx 서브시스템과 이미징 서브시스템 사이에 Gasket이라는 블럭이 있다. 여기에는 관련된 주변 디바이스의 다양한 기능을 제어하기 위한 범용 레지스터가 포함되어 있으며, 사용 사례에 따라 적절하게 구성해야 한다.

- Rx 컨트롤러, DPHY, Gasket를 활성화한다.

3.2.5 DPHY high-speed settle timer

RX_HS_SETTLE [7:0]은 각 레인의 MIPI 데이터 속도에 따라 설정되어야 한다(Table 13 참조).

Table 13. RX_HS_SETTLE setting for different data rates

| Data rate (Mbit/s) | RX_HS_SETTLE [7:0] |

|---|---|

| 1500 | 33 |

| 1490~1450 | 32 |

| 1440~1410 | 31 |

| 1400~1360 | 30 |

| 1350~1320 | 29 |

| 1310~1270 | 28 |

| 1260~1230 | 27 |

| 1220~1180 | 26 |

| 1170~1130 | 25 |

| 1120~1090 | 24 |

| 1080~1040 | 23 |

| 1030~1000 | 22 |

| 990~950 | 21 |

| 940~910 | 20 |

| 900~860 | 19 |

| 850~820 | 18 |

| 810~770 | 17 |

| 760~730 | 16 |

| 720~680 | 15 |

| 670~640 | 14 |

| 630~590 | 13 |

| 580~550 | 12 |

| 540~500 | 11 |

| 490~460 | 10 |

| 450~410 | 9 |

| 400~370 | 8 |

| 360~320 | 7 |

| 310~280 | 6 |

| 270~230 | 5 |

| 220~190 | 4 |

| 180~140 | 3 |

| 130~100 | 2 |

| 90~80 | 1 |

3.2.6 Register definition

이 섹션에서는 사용자가 새로운 카메라를 포팅하기 위해 주의해야 하는 일부 레지스터 필드가 나열되어 있다. 레지스터에 대한 더 많은 정보는 i.MX 8MM, i.MX 8MN, i.MX 8MP Reference Manual을 참조한다.

MIPI CSI-2 컨트롤러에 대한 기본 주소는 다음과 같다:

- i.MX 8MN/8MM CSI-2 Port 1: 32E3_0000h

- i.MX 8MP CSI-2 Port 1: 32E4_0000h

- i.MX 8MP CSI-2 Port 2: 32E5_0000h

▶ MIPI_CSIx_CSIS_COMMON_CTRL 레지스터: 4h 오프셋

Table 14. MIPI_CSIx_CSIS_COMMON_CTRL register

| Field | Description |

|---|---|

| 9-8 LANE_NUMBER |

데이터 레인 수 00 1 data lane 01 2 data lane 10 3 data lane 11 4 data lane |

▶ MIPI_CSIx_INTERRUPT_MASK_0 레지스터: 10h 오프셋

Table 15. MIPI_CSIx_INTERRUPT_MASK_0

| Field | Description |

|---|---|

| 24 MSK_FRAMESTART |

FS 패킷 수신, CH0 0 Disable (masked) 1 Enable (unmasked) |

| 20 MSK_FRAMEEND |

FE 패킷 수신, CH0 0 Disable (masked) 1 Enable (unmasked) |

| 19-16 MSK_ERR_SOT_HS |

전송 시작 오류 [Lane3, Lane2, Lane1, Lane0] 0 Disable (masked) 1 Enable (unmasked) |

| 12 MSK_ERR_LOST_FS |

Frame Start 패킷 손실, CH0 0 Disable (masked) 1 Enable (unmasked) |

| 8 MSK_ERR_LOST_FE |

Frame End 패킷 손실, CH0 0 Disable (masked) 1 Enable (unmasked) |

| 4 MSK_ERR_OVER |

Image FIFO 오버플로우 인터럽트 0 Disable (masked) 1 Enable (unmasked) |

| 3 MSK_ERR_WRONG_CFG |

잘못된 구성 0 Disable (masked) 1 Enable (unmasked) |

| 2 MSK_ERR_ECC |

ECC 에러 0 Disable (masked) 1 Enable (unmasked) |

| 1 MSK_ERR_CRC |

CRC 에러 0 Disable (masked) 1 Enable (unmasked) |

| 0 MSK_ERR_ID |

Unknown ID 에러 0 Disable (masked) 1 Enable (unmasked) |

▶ MIPI_CSIx_INTERRUPT_SOURCE_0 레지스터: 14h 오프셋

Table 16. MIPI_CSIx_INTERRUPT_SOURCE_0

| Field | Description |

|---|---|

| 24 FRAME_START |

FS 패킷 수신, CH0 |

| 20 FRAME_END |

FE 패킷 수신, CH0 |

| 19-16 ERR_SOT_HS |

전송 시작 오류 [Lane3, Lane2, Lane1, Lane0] 0 Disable (masked) 1 Enable (unmasked) |

| 12 ERR_LOST_FS |

Frame Start 패킷 손실 감지, CH0 이 필드는 프레임 시작 패킷 없이 이미지 데이터가 수신된 경우 '1'로 설정된다. |

| 8 ERR_LOST_FE |

Frame End 패킷 손실 감지, CH0 이 필드는 프레임 종료 패킷 없이 이미지 데이터가 수신된 경우 '1'로 설정된다. |

| 4 ERR_OVER |

Image FIFO에서 오버플로우 발생 외부 대역폭은 내부 대역폭보다 빨라야 한다. 그러나 이미지 FIFO는 사용자의 잘못으로 오버플로우될 수 있다. 오버플로우를 방지하는 방법에는 두 가지가 있다.

|

| 3 ERR_WRONG_CFG |

잘못된 구성 잘못된 데이터 유형이나 가상 채널 ID로 인해 수신된 패킷이 ISP나 CAM 인터페이스 채널에 할당되지 않았다. |

| 2 ERR_ECC |

ECC 에러 |

| 1 ERR_CRC |

CRC 에러 |

| 0 ERR_ID |

Unknown ID 에러 |

▶ MIPI_CSIx_DPHY_STATUS 레지스터: 20h 오프셋

Table 17. MIPI_CSIx_DPHY_STATUS

| Field | Description |

|---|---|

| 11-8 ULPSDAT |

UPLS의 Data lane [3:0] [11] : data lane 3 [10] : data lane 2 [9] : data lane 1 [8] : data lane 0 0 Not ULPS 1 ULPS |

| 7-4 STOPSTATEDAT |

Stop State의 Data lane [3:0] [7] : data lane 3 [6] : data lane 2 [5] : data lane 1 [4] : data lane 0 0 Not Stop state 1 Stop state |

| 1 ULPSCLK |

0 Not ULPS 1 ULPS |

| 0 STOPSTATECLK |

Stop State의 Clock lane 0 Not Stop state 1 Stop state |

▶ MIPI_CSIx_DPHY_COMMON_CTRL 레지스터: 24h 오프셋

Table 18. MIPI_CSIx_DPHY_COMMON_CTRL register

| Field | Description |

|---|---|

| 31-24 HSSETTLE[7:0] |

HS-RX settle 타임 컨트롤 Ths-settle에 대한 Slave Clock Lane Control. Section 3.2.5 참조. |

| 4-1 ENABLE_DAT[3:0] |

DPHY 데이터 레인 활성화 [3] : data lane 3 [2] : data lane 2 [1] : data lane 1 [0] : data lane 0 0 Disable 1 Enable |

| 0 ENABLE_CLK |

DPHY 클럭 레인 활성 0 Disable 1 Enable |

▶ MIPI_CSIx_ISP_CONFIG0 레지스터: 40h 오프셋

Table 19. MIPI_CSIx_ISP_CONFIG0

| Field | Description |

|---|---|

| 13-12 PIXEL_MODE |

픽셀 모드 선택 01 : dual pixel mode (YUV422) 00 : single pixel mode |

| 7-2 DATAFORMAT[5:0] |

Image Data Format 0x18 - YUV420 (8bit) 0x19 - YUV420 (10bit) 0x1A - YUV420 (8bit legacy) 0x1C - YUV420 (8bit CSPS) 0x1D - YUV420 (10bit CSPS) 0x1E - YUV422 (8bit) 0x1F - YUV422 (10bit) 0x20 - (NOT SUPPORTED) RGB444 0x21 - (NOT SUPPORTED) RGB555 0x22 - RGB565 0x23 - RGB666 0x24 - RGB888 0x28 - RAW6 0x29 - RAW7 0x2A - RAW8 0x2B - RAW10 0x2C - RAW12 0x2D - RAW14 0x30 - User defined 1 0x31 - User defined 2 0x32 - User defined 3 0x33 - User defined 4 0x34 - User defined 5 0x35 - User defined 6 0x36 - User defined 7 0x37 - User defined 8 참고: 설명되지 않은 유형은 무시된다. |

▶ MIPI_CSIx_ISP_RESOLUTION0 레지스터: 44h 오프셋

Table 20. MIPI_CSIx_ISP_RESOLUTION0

| Field | Description |

|---|---|

| 31-16 VRESOL |

Vertical Image 해상도 입력 범위: 0x0001 ~ 0xFFFF |

| 15-0 HRESOL |

Horizontal Image 해상도 HRESOL 값은 표준 사양의 조건을 준수해야 하며 4의 배수이어야 한다. 입력 범위: 0x0004 ~ 0xFFFC |

Gasket의 기본 주소는 다음과 같다:

- i.MX 8MN CSI-2 Port 1용 Gasket 0: 32E2_8060h

- i.MX 8MP CSI-2 Port 1용 Gasket 0: 32EC_0060h

- i.MX 8MP CSI-2 Port 2용 Gasket 1: 32EC_0090h

▶ GASKET_x_CTRL 레지스터: 0h 오프셋

Table 21. MIPI_CSIx_ISP_RESOLUTION0

| Field | Description |

|---|---|

| 13-8 GASKET_x_DATA_TYPE |

Gasket x 데이터 유형 011000b - YUV420 8-bit 011001b - YUV420 10-bit 011010b - Legacy YUV420 8-bit 011100b - YUV420 8-bit(Chroma Shifted Pixel Sampling) 011101b - YUV420 10-bit(Chroma Shifted Pixel Sampling) 011110b - YUV422 8-bit 011111b - YUV422 10-bit 100010b - RGB565 100011b - RGB666 100100b - RGB888 101000b - RAW6 101001b - RAW7 101010b - RAW8 101011b - RAW10 101100b - RAW12 101101b - RAW14 |

| 7-6 GASKET_x_INTER_MODE |

Gasket x 인터레이스 모드 00b - not interlaced 01b - interlaced left 10b - interlaced right 11b - reserved |

| 1 GASKET_x_DOUBLE_COMP |

Gasket x 더블 컴포넌트 활성화 0b - YUV422용 픽셀 클럭당 Gasket x 입력 단일 컴포넌트 1b - YUV422용 픽셀 클럭당 Gasket x 입력 더블 컴포넌트 |

참고:

GASKET_x_INTER_MODE 필드는 인터레이스된 이미지 데이터를 디인터페이스 기능이 지원되는 ISI로 전송하도록 구성되어야 한다.

▶ GASKET_x_HSIZE 레지스터: 4h 오프셋

Table 22. GASKET_x_HSIZE

| Field | Description |

|---|---|

| 31-0 GASKET_x_HSIZE |

Gasket x 비디오 Horizontal 크기 (픽셀 카운트) |

▶ GASKET_x_VSIZE 레지스터: 8h 오프셋

Table 23. GASKET_x_VSIZE

| Field | Description |

|---|---|

| 31-0 GASKET_x_VSIZE |

Gasket x 비디오 Vertical 크기 (라인 카운트) |

▶ GASKET_x_ISI_PIXEL_CNT 레지스터: 1Ch 오프셋

Table 24. GASKET_x_ISI_PIXEL_CNT

| Field | Description |

|---|---|

| 31-0 GASKET_x_ISI_PIXEL_CNT |

ISI 픽셀 카운트 상태에 대한 Gasket x 출력 |

▶ GASKET_x_ISI_LINE_CNT 레지스터: 20h 오프셋

Table 25. GASKET_x_ISI_LINE_CNT

| Field | Description |

|---|---|

| GASKET_x_ISI_LINE_CNT | ISI 라인 카운트 상태에 대한 Gasket x 출력 |

'NXP i.MX SoC Family > i.MX 8M Series MIPI Capture System' 카테고리의 다른 글

| i.MX 8M Series MIPI Capture System(AN13857) - MIPI capture capabilities (0) | 2023.04.10 |

|---|---|

| i.MX 8M Series MIPI Capture System(AN13857) - Imaging subsystem (0) | 2023.04.06 |

| i.MX 8M Series MIPI Capture System(AN13857) - Overview (0) | 2023.04.03 |

| i.MX 8M Series MIPI Capture System(AN13857) - Introduction (0) | 2023.04.03 |

| i.MX 8M Series MIPI Capture System(AN13857) (0) | 2023.04.03 |